新エネルギー・産業技術総合開発機構(NEDO http://www.nedo.go.jp )は、極低電力LSIの実現に不可欠な半導体構造の微細化に対応できる、半導体デバイスプロセス基盤技術を確立するための次世代半導体微細加工・評価基盤技術の開発に着手した。

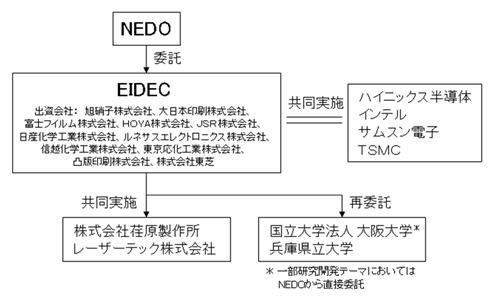

EUVL基盤開発センター(EIDEC)、大阪大学などと共同で、極端紫外光(EUV)リソグラフィに必要なマスクブランクやマスクパターンの欠陥検査・評価・同定技術、およびレジスト材料の露光性能やアウトガス評価を含めた評価技術や材料開発など、回路線幅16nm以細に対応可能な技術の確立に向けて研究開発に取り組む。研究期間は2015年度まで。今年度事業規模は約37億円を予定している。

情報家電、コンピュータ、通信装置、自動車、医療機器などの先端産業の国際競争力強化のために、半導体LSIの微細化技術は不可欠な基盤技術。これまで、微細化技術の進展による半導体LSIの集積度は、3年で4倍という急速な早さで推移してきており、2010年には、回路線幅45nm世代の製品が量産され始めた。今後も情報家電やロボットなどのシステムに求められる半導体LSIの高集積化・低コスト化および低消費電力化を同時に実現するためには、さらなる微細化が必要となる。しかし、次世代リソグラフィの最有力候補と位置付けられているEUVリソグラフィにおいて、マスク技術や関連検査技術、レジスト材料等に解決すべき課題が残されている。

そこで、本プロジェクトでは、これらの課題解決に産学官連携の研究体制で取り組み、回路線幅16nm以細で、高精度・低欠陥マスクを実現し、高解像度、低LWR(Line Width Roughness)、高感度および低アウトガスを満たすレジスト材料を実現する半導体デバイスプロセス基盤技術を確立することを目的とする。